Date:- 4th June, 2014

Data Sheet Issue:- 4

# Phase Control Thyristor Types N0465WN140 and N0465WN160

# **Absolute Maximum Ratings**

|           | VOLTAGE RATINGS                                 | MAXIMUM<br>LIMITS | UNITS |

|-----------|-------------------------------------------------|-------------------|-------|

| $V_{DRM}$ | Repetitive peak off-state voltage, (note 1)     | 1400-1600         | ٧     |

| $V_{DSM}$ | Non-repetitive peak off-state voltage, (note 1) | 1500-1700         | V     |

| $V_{RRM}$ | Repetitive peak reverse voltage, (note 1)       | 1400-1600         | V     |

| $V_{RSM}$ | Non-repetitive peak reverse voltage, (note 1)   | 1500-1700         | V     |

|                       | OTHER RATINGS                                                             |                    | MAXIMUM<br>LIMITS   | UNITS  |

|-----------------------|---------------------------------------------------------------------------|--------------------|---------------------|--------|

| I <sub>T(AV)M</sub>   | Maximum average on-state current, T <sub>sink</sub> =55°C, (              | note 2)            | 465                 | Α      |

| $I_{T(AV)M}$          | Maximum average on-state current. T <sub>sink</sub> =85°C, (              | note 2)            | 315                 | Α      |

| $I_{T(AV)M}$          | Maximum average on-state current. T <sub>sink</sub> =85°C, (              | note 3)            | 180                 | Α      |

| I <sub>T(RMS)M</sub>  | Nominal RMS on-state current, T <sub>sink</sub> =25°C, (note              | 2)                 | 920                 | Α      |

| I <sub>T(d.c.)</sub>  | D.C. on-state current, T <sub>sink</sub> =25°C, (note 4)                  |                    | 795                 | Α      |

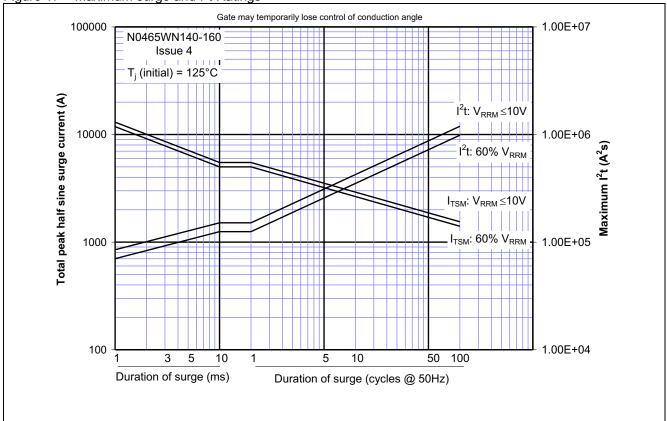

| I <sub>TSM</sub>      | Peak non-repetitive surge $t_p$ =10ms, $V_m$ =60% $V_{RRM}$               | 4500               | Α                   |        |

| I <sub>TSM2</sub>     | Peak non-repetitive surge t <sub>p</sub> =10ms, V <sub>m</sub> ≤10V, (not | 5000               | Α                   |        |

| I <sup>2</sup> t      | $I^2$ t capacity for fusing $t_p$ =10ms, $V_m$ =60% $V_{RRM}$ , (no       | ote 5)             | 101×10 <sup>3</sup> | $A^2s$ |

| I <sup>2</sup> t      | $I^{2}t$ capacity for fusing $t_{p}$ =10ms, $V_{rm}$ ≤10V, (note 5)       |                    | 125×10 <sup>3</sup> | $A^2s$ |

| (-1:/-14)             | Cuitical mate of mice of an atota assument (mate C)                       | (continuous, 50Hz) | 125                 | Λ/     |

| (di/dt) <sub>cr</sub> | Critical rate of rise of on-state current (note 6)                        | (non-repetitive)   | 250                 | A/µs   |

| $V_{RGM}$             | Peak reverse gate voltage                                                 |                    | 5                   | V      |

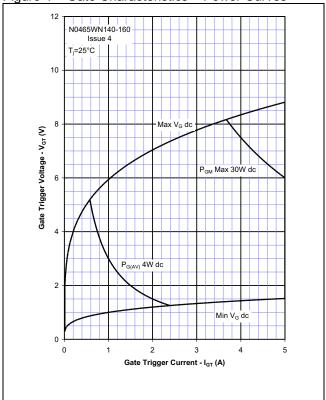

| $P_{G(AV)}$           | Mean forward gate power                                                   | 3                  | W                   |        |

| $P_GM$                | Peak forward gate power                                                   | 30                 | W                   |        |

| T <sub>j op</sub>     | Operating temperature range                                               | -60 to +125        | °C                  |        |

| T <sub>stg</sub>      | Storage temperature range                                                 |                    | -60 to +125         | °C     |

#### Notes:-

- 1) De-rating factor of 0.13% per °C is applicable for T<sub>i</sub> below 25°C.

- 2) Double side cooled, single phase; 50Hz, 180° half-sinewave.

- 3) Anode side cooled, single phase; 50Hz, 180° half-sinewave.

- 4) Double side cooled.

- 5) Half-sinewave, 125°C T<sub>i</sub> initial.

- 6)  $V_D=67\% V_{DRM}$ ,  $I_{TM}=800A$ ,  $I_{FG}=2A$ ,  $t_r \le 0.5 \mu s$ ,  $T_{case}=125$ °C.

# **Characteristics**

|                       | PARAMETER                                  | MIN. | TYP. | MAX.  | TEST CONDITIONS (Note 1)                                                                                                                       | UNITS |

|-----------------------|--------------------------------------------|------|------|-------|------------------------------------------------------------------------------------------------------------------------------------------------|-------|

| $V_{TM}$              | Maximum peak on-state voltage              | -    | -    | 1.30  | I <sub>TM</sub> =465A                                                                                                                          | V     |

| $V_{TM}$              | Maximum peak on-state voltage              | -    | -    | 2.09  | I <sub>TM</sub> =1400A                                                                                                                         | V     |

| $V_{T0}$              | Threshold voltage                          | -    | -    | 0.90  |                                                                                                                                                | V     |

| r⊤                    | Slope resistance                           | -    | -    | 0.85  |                                                                                                                                                | mΩ    |

| (dv/dt) <sub>cr</sub> | Critical rate of rise of off-state voltage | 1000 | -    | -     | V <sub>D</sub> =67% V <sub>DRM</sub> , linear ramp, gate o/c                                                                                   | V/μs  |

| I <sub>DRM</sub>      | Peak off-state current                     | -    | -    | 50    | Rated V <sub>DRM</sub>                                                                                                                         | mA    |

| I <sub>RRM</sub>      | Peak reverse current                       | -    | -    | 50    | Rated V <sub>RRM</sub>                                                                                                                         | mA    |

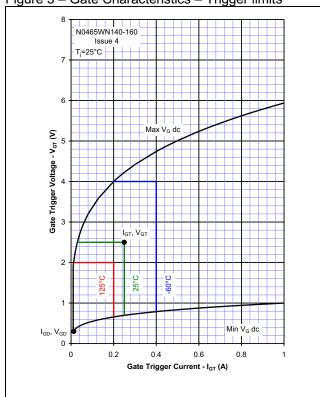

| $V_{GT}$              | Gate trigger voltage                       | -    | -    | 2.5   | T-25°C                                                                                                                                         | V     |

| I <sub>GT</sub>       | Gate trigger current                       | -    | -    | 250   | $T_j$ =25°C $V_D$ =10V, $I_T$ =3A                                                                                                              | mA    |

| $V_{GD}$              | Gate non-trigger voltage                   | -    | -    | 0.25  | Rated V <sub>DRM</sub>                                                                                                                         | V     |

| IH                    | Holding current                            | -    | -    | 250   | T <sub>j</sub> =25°C                                                                                                                           | mA    |

| t <sub>gd</sub>       | Gate-controlled turn-on delay time         | -    | -    | 2.0   | V <sub>D</sub> =67% V <sub>DRM</sub> , I <sub>T</sub> =450A, di/dt=10A/μs,<br>I <sub>FG</sub> =2A, t <sub>r</sub> =0.5μs, T <sub>j</sub> =25°C | μs    |

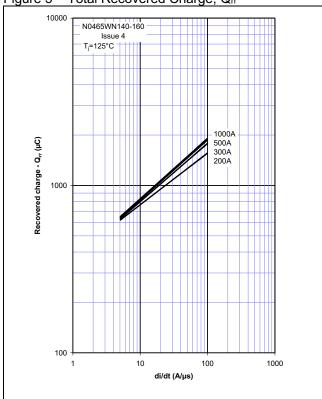

| $Q_{rr}$              | Recovered charge                           | -    | 700  | 800   |                                                                                                                                                | μC    |

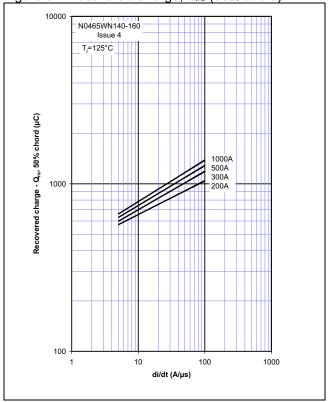

| Q <sub>ra</sub>       | Recovered charge, 50% Chord                | -    | 650  | -     | <br>  I <sub>TM</sub> =300A, t <sub>p</sub> =500μs, di/dt=10A/μs,                                                                              | μC    |

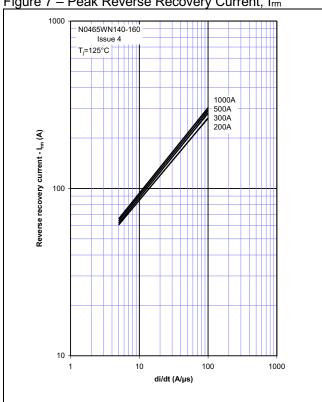

| Irr                   | Reverse recovery current                   | -    | 85   | -     | V <sub>r</sub> =100V                                                                                                                           | Α     |

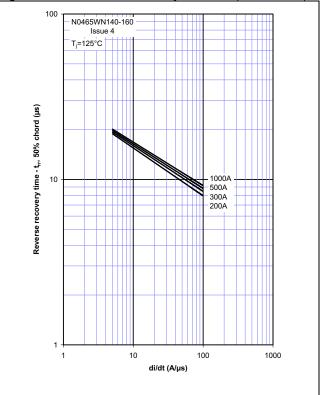

| t <sub>rr</sub>       | Reverse recovery time                      | -    | 15   | -     |                                                                                                                                                | μs    |

| +                     | Turn-off time                              | -    | -    | 120   | $I_{TM}$ =300A, $t_p$ =500 $\mu$ s, di/dt=10A/ $\mu$ s, $V_r$ =100V, $V_{dr}$ =67% $V_{DRM}$ , d $V_{dr}$ /dt=20V/ $\mu$ s                     | μs    |

| t <sub>q</sub>        | Turn-on time                               | ı    | -    | 150   | $I_{TM}$ =300A, $t_p$ =500 $\mu$ s, di/dt=10A/ $\mu$ s, $V_r$ =100V, $V_{dr}$ =67% $V_{DRM}$ , d $V_{dr}$ /dt=200V/ $\mu$ s                    | μs    |

|                       |                                            | ı    | -    | 0.080 | Double side cooled                                                                                                                             | K/W   |

| $R_{thJK}$            | Thermal resistance, junction to heatsink   | -    | -    | 0.174 | Anode side cooled                                                                                                                              |       |

|                       |                                            | -    | -    | 0.146 | Cathode side cooled                                                                                                                            | K/W   |

| F                     | Mounting force                             | 5    | -    | 7     | Note 2.                                                                                                                                        | kN    |

| $W_t$                 | Weight                                     | -    | 70   | -     |                                                                                                                                                | g     |

- Notes:- 1) Unless otherwise indicated  $T_j$ =125°C.

- 2) For other clamp forces, please consult factory.

#### **Notes on Ratings and Characteristics**

#### 1.0 Voltage Grade Table

| Voltage Grade | V <sub>DRM</sub> V <sub>RRM</sub><br>V | V <sub>DSM</sub> V <sub>RSM</sub><br>V | V <sub>D</sub> V <sub>R</sub><br>DC V |

|---------------|----------------------------------------|----------------------------------------|---------------------------------------|

| 14            | 1400                                   | 1500                                   | 1050                                  |

| 16            | 1600                                   | 1700                                   | 1200                                  |

#### 2.0 Extension of Voltage Grades

This report is applicable to other voltage grades when supply has been agreed by Sales/Production.

#### 3.0 De-rating Factor

A blocking voltage de-rating factor of 0.13%/°C is applicable to this device for T<sub>j</sub> below 25°C.

# 4.0 Repetitive dv/dt

Standard dv/dt is 1000V/µs.

#### 5.0 Snubber Components

When selecting snubber components, care must be taken not to use excessively large values of snubber capacitor or excessively small values of snubber resistor. Such excessive component values may lead to device damage due to the large resultant values of snubber discharge current. If required, please consult the factory for assistance.

#### 6.0 Rate of rise of on-state current

The maximum un-primed rate of rise of on-state current must not exceed 250A/µs at any time during turn-on on a non-repetitive basis. For repetitive performance, the on-state rate of rise of current must not exceed 125A/µs at any time during turn-on. Note that these values of rate of rise of current apply to the total device current including that from any local snubber network.

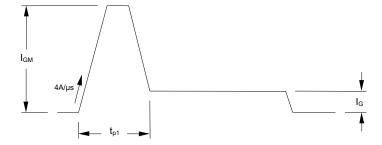

### 7.0 Gate Drive

The nominal requirement for a typical gate drive is illustrated below. An open circuit voltage of at least 30V is assumed. This gate drive must be applied when using the full di/dt capability of the device.

The magnitude of  $I_{GM}$  should be between five and ten times  $I_{GT}$ , which is shown on page 2. Its duration  $(t_{p1})$  should be 20µs or sufficient to allow the anode current to reach ten times  $I_L$ , whichever is greater. Otherwise, an increase in pulse current could be needed to supply the necessary charge to trigger. The 'back-porch' current  $I_G$  should remain flowing for the same duration as the anode current and have a magnitude in the order of 1.5 times  $I_{GT}$ .

### 8.0 Computer Modelling Parameters

# 8.1 Device Dissipation Calculations

$$I_{AV} = \frac{-V_{T0} + \sqrt{{V_{T0}}^2 + 4 \cdot ff^2 \cdot r_T \cdot W_{AV}}}{2 \cdot ff^2 \cdot r_T} \qquad \text{and:} \qquad W_{AV} = \frac{\Delta T}{R_{th}} \\ \Delta T = T_{j \max} - T_K$$

Where  $V_{T0}=0.90V$ ,  $r_T=0.85m\Omega$ ,

$R_{\it th}$  = Supplementary thermal impedance, see table below and

ff = Form factor, see table below.

| Supplementary Thermal Impedance |        |        |        |        |        |        |        |

|---------------------------------|--------|--------|--------|--------|--------|--------|--------|

| Conduction Angle                | 30°    | 60°    | 90°    | 120°   | 180°   | 270°   | d.c.   |

| Square wave Double Side Cooled  | 0.1071 | 0.0996 | 0.0947 | 0.0912 | 0.0867 | 0.0825 | 0.0800 |

| Square wave Anode Side Cooled   | 0.2022 | 0.1951 | 0.1903 | 0.1869 | 0.1823 | 0.1780 | 0.1740 |

| Square wave Cathode Side Cooled | 0.1740 | 0.1671 | 0.1623 | 0.1589 | 0.1541 | 0.1497 | 0.1460 |

| Sine wave Double Side Cooled    | 0.0996 | 0.0918 | 0.0880 | 0.0854 | 0.0810 |        |        |

| Sine wave Anode Side Cooled     | 0.1954 | 0.1878 | 0.1840 | 0.1813 | 0.1755 |        |        |

| Sine wave Cathode Side Cooled   | 0.1675 | 0.1601 | 0.1562 | 0.1504 | 0.1473 |        |        |

| Form Factors     |      |      |      |      |      |      |      |

|------------------|------|------|------|------|------|------|------|

| Conduction Angle | 30°  | 60°  | 90°  | 120° | 180° | 270° | d.c. |

| Square wave      | 3.46 | 2.45 | 2    | 1.73 | 1.41 | 1.15 | 1    |

| Sine wave        | 3.98 | 2.78 | 2.22 | 1.88 | 1.57 |      |      |

### 8.2 Calculating V<sub>T</sub> using ABCD Coefficients

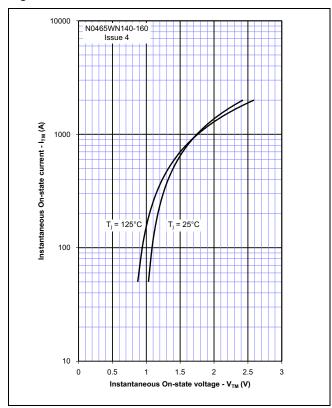

The on-state characteristic I<sub>T</sub> vs. V<sub>T</sub>, on page 7 is represented in two ways;

- (i) the well established  $V_{T0}$  and  $r_T$  tangent used for rating purposes and

- (ii) a set of constants A, B, C, D, forming the coefficients of the representative equation for  $V_T$  in terms of  $I_T$  given below:

$$V_T = A + B \cdot \ln(I_T) + C \cdot I_T + D \cdot \sqrt{I_T}$$

The constants, derived by curve fitting software, are given below for both hot and cold characteristics. The resulting values for  $V_T$  agree with the true device characteristic over a current range, which is limited to that plotted.

| 25°C Coefficients |                           | 125°C Coefficients |                           |  |

|-------------------|---------------------------|--------------------|---------------------------|--|

| Α                 | 0.8848613                 | Α                  | 0.6889269                 |  |

| В                 | 0.02895245                | В                  | 0.03541837                |  |

| С                 | 6.603509×10 <sup>-4</sup> | С                  | 7.974785×10 <sup>-4</sup> |  |

| D                 | 5.731747×10 <sup>-5</sup> | D                  | 8.475309×10 <sup>-4</sup> |  |

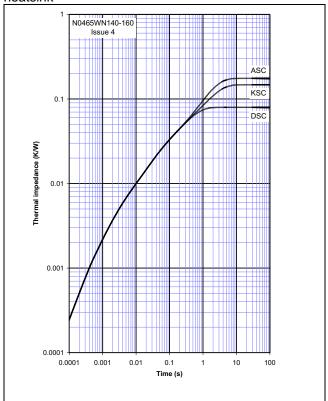

# 8.3 D.C. Thermal Impedance Calculation

$$r_t = \sum_{p=1}^{p=n} r_p \cdot \left(1 - e^{\frac{-t}{\tau_p}}\right)$$

Where p = 1 to n, n is the number of terms in the series and:

t = Duration of heating pulse in seconds.

$r_{t}$  = Thermal resistance at time t.

$r_p$  = Amplitude of  $p_{th}$  term.

$\tau_p$  = Time Constant of  $r_{th}$  term.

The coefficients for this device are shown in the tables below:

| D.C. Double Side Cooled |            |            |                          |                          |  |  |

|-------------------------|------------|------------|--------------------------|--------------------------|--|--|

| Term                    | 1          | 2          | 3                        | 4                        |  |  |

| $r_p$                   | 0.05247007 | 0.01740139 | 6.523029×10 <sup>3</sup> | 3.104404×10 <sup>3</sup> |  |  |

| $	au_{p}$               | 0.4423651  | 0.07342380 | 0.01331570               | 1.856622×10 <sup>3</sup> |  |  |

| D.C. Anode Side Cooled |           |            |                          |                          |  |  |

|------------------------|-----------|------------|--------------------------|--------------------------|--|--|

| Term                   | 1         | 2          | 3                        | 4                        |  |  |

| $r_p$                  | 0.1393116 | 0.02365745 | 8.492782×10 <sup>3</sup> | 3.570429×10 <sup>3</sup> |  |  |

| $	au_p$                | 1.681507  | 0.1246687  | 0.01741510               | 2.156006×10 <sup>3</sup> |  |  |

| D.C. Cathode Side Cooled |           |            |            |                          |  |  |

|--------------------------|-----------|------------|------------|--------------------------|--|--|

| Term                     | 1         | 2          | 3          | 4                        |  |  |

| $r_p$                    | 0.1014680 | 0.02735631 | 0.01363533 | 4.334170×10 <sup>3</sup> |  |  |

| $	au_{p}$                | 2.009533  | 0.2094914  | 0.02992179 | 2.532787×10 <sup>3</sup> |  |  |

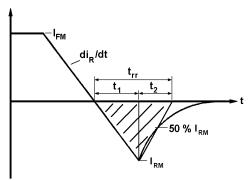

# 9.0 Reverse recovery ratings

(i)  $Q_{\text{ra}}$  is based on 50%  $I_{\text{rm}}$  chord as shown in Diagram

Diagram 1

(ii)  $Q_{rr}$  is based on a 150 $\mu$ s integration time i.e.

$$Q_{rr} = \int_{0}^{150\,\mu s} i_{rr}.dt$$

(iii)

$$K Factor = \frac{t_1}{t_2}$$

# **Curves**

Figure 1 – On-state characteristics of Limit device

Figure 2 – Transient thermal impedance junction to heatsink

Figure 3 – Gate Characteristics – Trigger limits

Figure 4 – Gate Characteristics – Power Curves

Figure 6 – Recovered Charge, Qra (50% chord)

Figure 7 - Peak Reverse Recovery Current, Im

Figure 8 – Maximum Recovery Time, t<sub>rr</sub> (50% chord)

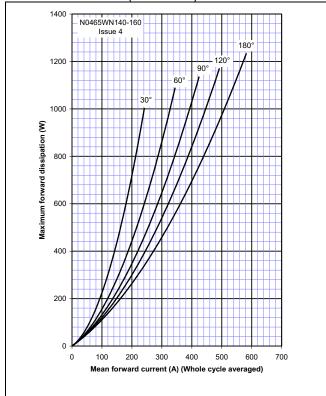

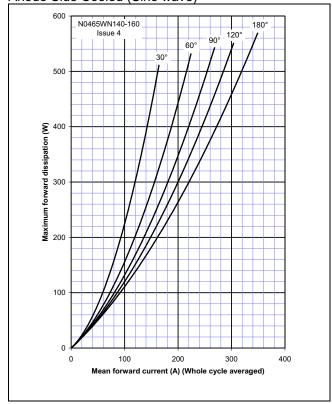

Figure 9 – On-state current vs. Power dissipation – Double Side Cooled (Sine wave)

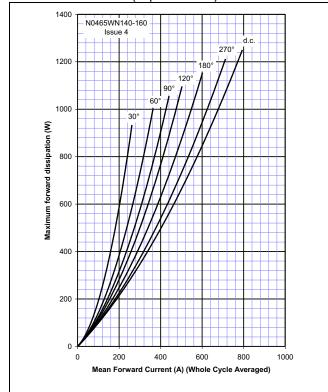

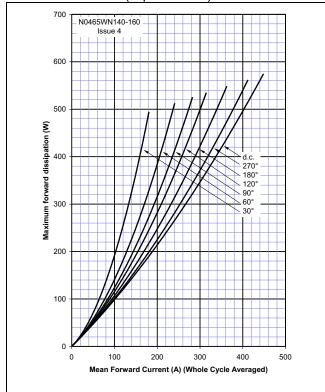

Figure 11 – On-state current vs. Power dissipation – Double Side Cooled (Square wave)

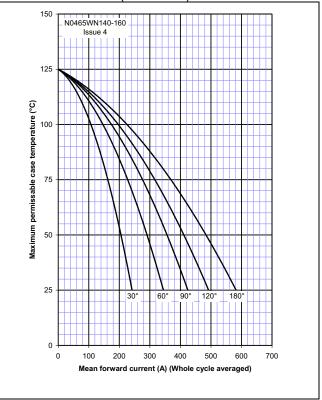

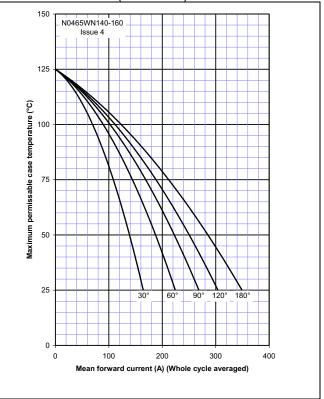

Figure 10 – On-state current vs. Case temperature – Double Side Cooled (Sine wave)

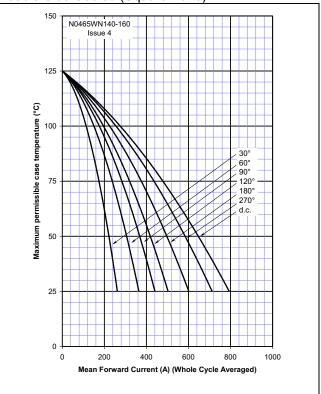

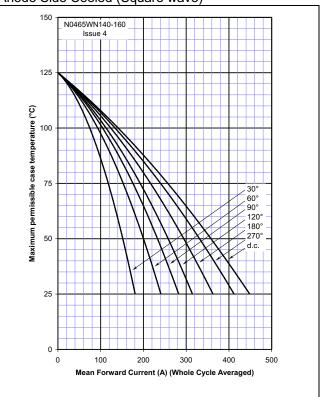

Figure 12 – On-state current vs. Case temperature – Double Side Cooled (Square wave)

Figure 13 – On-state current vs. Power dissipation – Anode Side Cooled (Sine wave)

Figure 15 – On-state current vs. Power dissipation – Anode Side Cooled (Square wave)

Figure 14 – On-state current vs. Case temperature – Anode Side Cooled (Sine wave)

Figure 16 – On-state current vs. Case temperature – Anode Side Cooled (Square wave)

Figure 17 – Maximum surge and I<sup>2</sup>t Ratings

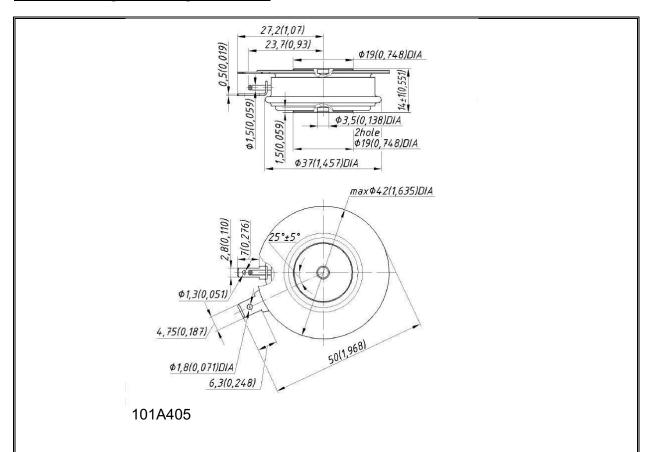

# **Outline Drawing & Ordering Information**

| ORDER              | NG INFORMATION     | (Please quote 10 digit code                      | e as below)              |

|--------------------|--------------------|--------------------------------------------------|--------------------------|

| N0465              | WN                 | ##                                               | 0                        |

| Fixed<br>Type Code | Fixed outline code | Voltage code<br>V <sub>DRM</sub> /100<br>14 & 18 | Fixed turn-off time code |

Order code: N0465WN160 – 1600V  $V_{\text{DRM}},\,V_{\text{RRM}},\,14\text{mm}$  clamp height capsule.

#### **IXYS Semiconductor GmbH**

Edisonstraße 15 D-68623 Lampertheim Tel: +49 6206 503-0 Fax: +49 6206 503-627 E-mail: marcom@ixys.de

#### IXYS UK Westcode Ltd

Langley Park Way, Langley Park, Chippenham, Wiltshire, SN15 1GE. Tel: +44 (0)1249 444524 Fax: +44 (0)1249 659448 E-mail: sales@ixysuk.com

### IXYS Corporation

1590 Buckeye Drive Milpitas CA 95035-7418 Tel: +1 (408) 457 9000 Fax: +1 (408) 496 0670 E-mail: sales@ixys.net

www.ixysuk.com

www.ixys.com

#### IXYS Long Beach

© IXYS UK Westcode Ltd.

IXYS Long Beach, Inc 2500 Mira Mar Ave, Long Beach CA 90815

Tel: +1 (562) 296 6584 Fax: +1 (562) 296 6585

E-mail: <a href="mailto:service@ixyslongbeach.com">service@ixyslongbeach.com</a>

The information contained herein is confidential and is protected by Copyright. The information may not be used or disclosed except with the written permission of and in the manner permitted by the proprietors IXYS UK Westcode Ltd.

In the interest of product improvement, IXYS UK Westcode Ltd reserves the right to change specifications at any time without prior notice.

Devices with a suffix code (2-letter, 3-letter or letter/digit/letter combination) added to their generic code are not necessarily subject to the conditions and limits contained in this report.